| Metric Bolt Torque Table Estimated with clamp load as 75% of proof load as specified in ISO 898-1 |

||||||

| Property Class |

8.8 | 10.9 | 12.9 Socket Head Cap Screw |

|||

| Minimum Tensile Strength MPa |

M6 – M16: 800 M20 – M30: 830 |

1040 | 1220 | |||

| Nominal Size and Thread Pitch |

Bolt Torque Specs in Newton Meters – Nm | |||||

| Dry | Lubed | Dry | Lubed | Dry | Lubed | |

| M5 x 0.80 | 6.1 | 4.6 | 8.8 | 6.7 | 10.3 | 7.7 |

| M6 x 1.00 | 10.4 | 7.8 | 15 | 11.2 | 17.6 | 13.1 |

| M7 x 1.00 | 17.6 | 13.1 | 25.1 | 18.9 | 29.4 | 22 |

| M8 x 1.25 | 25.4 | 19.1 | 37.6 | 27.3 | 42.6 | 32.1 |

| M10 x 1.50 | 50 | 38 | 72 | 54 | 84 | 64 |

| M12 x 1.75 | 88 | 66 | 126 | 94 | 146 | 110 |

| M14 x 2.00 | 141 | 106 | 201 | 150 | 235 | 176 |

| M16 x 2.00 | 218 | 164 | 312 | 233 | 365 | 274 |

| M18 x 2.50 | 301 | 226 | 431 | 323 | 504 | 378 |

| M20 x 2.50 | 426 | 319 | 609 | 457 | 712 | 534 |

| M22 x 2.50 | 580 | 435 | 831 | 624 | 971 | 728 |

| M24 x 3.00 | 736 | 552 | 1052 | 789 | 1231 | 923 |

| M27 x 3.00 | 1079 | 809 | 1544 | 1158 | 1805 | 1353 |

| M30 x 3.50 | 1463 | 1097 | 2092 | 1570 | 2446 | 1834 |

| M33 x 3.50 | 1990 | 1493 | 2849 | 2137 | 3328 | 2497 |

| M36 x 4.00 | 2557 | 1918 | 3659 | 2744 | 4276 | 3208 |

All posts by Alex Martin

World’s first long-range all-electric BYD Double-Decker buses introduced in London

London has become the first city to have on its revenue services routers, world’s first zero-emission, long-range, all-electric BYD Double-Decker buses.

The move by Transport for London (TfL) has been pegged by many as rather a bold move. The first BYD Double-Decker bus was deployed on its route with a special ceremony at London city hall with London’s Deputy Mayor of Environment and Energy, Matthew Pencharz formally receiving the first bus from BYD Europe.

Pencharz during the event that the running costs of these buses as well as some of the maintenance and operations cost are much lower than currently used buses. With zero-emission and zero-tailpipe-pollution, there is a huge environmental benefit specifically for London where pollution levels are relatively high compared to some similarly sized and populated cities around the world.

As the plan goes, currently TfL is commissioning five of the all-electric double decker buses on Route 98 operated on behalf of TfL by Metroline. Route 98 was chosen given its status as a pollution hotspot in the city.

BDY Europe will be providing support to TfL and Metroline for installation of fast charging equipment at Metroline’s Willesden Bus Garage in north London. Additionally, BYD will provide driver training for the bus operators.

BYD, the world’s largest electric vehicle manufacturer, designed and developed the vehicles to Transport of London’s specifications. The five buses scheduled for deployment are more than 33 feet long and feature air conditioning, seats for 54 passengers with space for 27 standing passengers (81 total).

The buses are equipped with BYD-designed and built Iron-Phosphate batteries, delivering 345 kWh of power that come with a Industry-benchmark 12 year battery warranty, the longest electric battery warranty available. The batteries can power the bus for over 24 hours and up to 190 miles of typical urban driving on the service routes with a single daily recharging requiring only four hours. TfL plans to charge the buses overnight using low-cost, off-peak electricity to provide additional cost savings.

Europe and Russia launch joint Space Mission to Mars

The Trace Gas Orbiter and Schiaparelli blasted off at 0931:42 GMT (5:31:42 a.m. EDT) from Complex 200 at the Baikonur Cosmodrome. Shortly after the fourth burn, ExoMars separated from Breeze-M and deployed its solar panels.

Luzin predicted the mission’s presumed success is likely to have benefits for Russia’s space program, which is struggling to stay competitive. “The second part of the ExoMars mission may be delayed to 2020”, said Igor Komarov, the chief of Roscosmos. In 2013, United States’ Beagle Probe disappeared, and ESA is trying to avoid these kinds of setbacks.

Dr Manish Patel, from the Open University, who is in charge of TGO’s ozone-mapping ultraviolet (UV) spectrometer instrument, said: “This is a fantastic mission, massive”.

TGO will photograph the Red Planet and analyse its air, splitting off from the lander dubbed Schiaparelli days before entering Mars’ atmosphere. Its task is to study life-hinting gases, such as methane, which is linked to life on Earth.

Its main job will be to test the descent and landing technology for ExoMars 2018, the next stage of the mission which will send a British-built rover to Mars in two years’ time.

The 660kg Schiaparelli will land on the Martian surface to collect meteorological and other types of data.

ESA said the rover landing “remains a significant challenge” however.

ExoMars, which cost the European Space Agency alone 1.3 billion euros ($1.44 billion), is the first interplanetary mission jointly undertaken by ESA and Roscomsos.

KAZAKHSTAN – Two robotic spacecraft on Monday began a seven-month journey to Mars as part of a European-Russian unmanned space mission to sniff out leads to life on the Red Planet. The second is planned for launch in 2018 and is a rover and surface science platform.

The joint investigation will involve the search for natural gases that scientists believe may be a sign of human life on Mars, The Australian reported.

“It’s been a long journey getting the first ExoMars mission to the launch pad, but thanks to the hard work and dedication of our global teams, a new era of Mars exploration is now within our reach”, Johann-Dietrich Woerner, director general of the European Space Agency, said in a statement.

Neither the ESA nor Roscosmos has the best track record when it comes to Martian missions, and for now, both space agencies are breathing a huge sigh of relief.

Traffic around Mars is about to get a bit heavier.

ExoMars is made up of 2 phases. Today’s launch brought along 2 different modules that make up the first phase: the Trace Gas Orbiter and the Entry, Descent and Landing Demonstrator Module known as “Schiaparelli”.

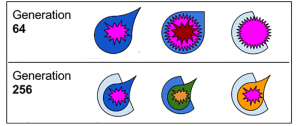

Genetic Algorithms, Making a Robot Evolve

Evolution is a fact of life, it is the defining characteristic of life itself, but that doesn’t mean a stupid robot can’t evolve. For his entry into the Hackaday Pi Zero contest, diemastermonkey is doing just that: evolution for robots built around microcontrollers and a Raspberry Pi.

The project is a physical extension to genetic algorithms. Just like DNA and proteins have no idea what they’re actually doing, microcontrollers don’t either. Instead of randomly switching up base pairs and amino acids, his project makes random connections pins depending on the values of those pins.

The potential of these randomly programmed robots is only as good as the fitness function, and so far he has seen some surprising success. When putting these algorithms into a microcontroller connected to a tilting table mechanism and a PIR sensor, the robot eventually settled on a bit of code that would keep a ball in motion. You can check out the video of this below.

3D Printed Robotic grippers

ZiLog Microcontrollers

ZiLOG, often seen as Zilog, is a manufacturer of 8-bit CPUs, and is most famous for its Intel 8080-compatible Z80 series. Zilog was incorporated in California in 1974 by Federico Faggin, who left Intel after working on the 8080, and the Z80 was a vast improvement over it (it was faster, etc.). The Z80 was a best seller because it was much cheaper than the 8080. It was used in the Nintendo Game Boy and many Texas Instruments graphing calculators as the main processor and in some newer game consoles as a secondary processor, like the Mega Drive.

After the Z80 Zilog introduced 16-bit and 32-bit processors, but these were not particularly successful, and the company refocused on the microcontroller market, producing both basic CPUs and application-specific integrated circuits/standard products (ASICs/ASSPs) built around a CPU core. As well as producing processors, Zilog has produced several other components. One of the most famous was the Z8530 serial communications controller as found on Sun SPARCstations and SPARCservers up to the SPARCstation 20.

The company became a subsidiary of Exxon in 1980, but the management and employees bought it back in 1989. It went public in 1991, but was acquired in 1998 by Texas Pacific Group, who, after chip prices plummeted, reorganized the company in a Chapter 11 bankruptcy in late 2001.

ARM architecture

The ARM architecture (originally the Acorn RISC Machine) is a 32-bit RISC processor architecture that is widely used in a number of embedded designs. Due to their power saving features, ARM CPUs are dominant in the mobile electronics market, where low-power is a critical design goal.

Today, the ARM family accounts for over 75% of all 32-bit embedded CPUs, making it one of the most prolific 32-bit architectures in the world. ARM CPUs are found in all corners of consumer electronics, from portable devices (PDAs, mobile phones, media players, handheld gaming units, and calculators) to computer peripherals (hard drives, desktop routers.) The most noticeable branch in this family nowadays is Intel’s XScale.

The ARM design was started in 1983 as a development project at Acorn Computers Ltd.

The team, led by Roger Wilson and Steve Furber, started development of what in some ways resembles an advanced MOS Technology 6502. Acorn had a long line of computers based on the 6502, so a chip that was similar to program could represent a significant advantage for the company.

The team completed development samples called ARM1 by 1985, and the first “real” production systems as ARM2 the following year. The ARM2 featured a 32-bit data bus, a 26-bit address space giving a 64 Mbyte address range and 16 32-bit registers. One of these registers served as the (word aligned) program counter with its top 6 bits and lowest 2 bits holding the processor status flags. The ARM2 was possibly the simplest useful 32-bit microprocessor in the world, with only 30,000 transistors (compare with Motorola’s four-year older 68000 with around 68,000). Much of this simplicity comes from not having microcode (which represents about 1/4 to 1/3rd of the 68000) and, like most CPUs of the day, not including any cache. This simplicity led to its low power usage, while performing better than the 286. A successor, ARM3, was produced with a 4KB cache which further improved performance.

In the late 1980s Apple Computer started working with Acorn on newer versions of the ARM core. The work was so important that Acorn spun off the design team in 1990 into a new company called Advanced RISC Machines. For this reason you often see ARM lengthened to Advanced RISC Machine instead of Acorn RISC Machine. Advanced RISC Machines became ARM Limited when the company floated on the London Stock Exchange and NASDAQ in 1998.

This work would eventually turn into the ARM6. The first models were released in 1991, and Apple used the ARM6-based ARM 610 as the basis for their Apple Newton PDA. In 1994, Acorn used the ARM 610 as the main CPU in their RiscPC computers.

The core has remained largely the same size throughout these changes. ARM2 had 30,000 transistors, while the ARM6 grew to only 35,000. The idea is that the end-user combines the ARM core with a number of optional parts to produce a complete CPU, one that can be built on old semiconductor fabs and still deliver lots of performance at a low cost.

The most successful implementation has been the ARM7TDMI with hundreds of millions sold in mobile phones, handheld video game systems, and Sega Dreamcasts. While ARM’s business has always been to sell IP cores, some of the licensees generated microcontrollers based on this core.

The Dreamcast features a SH4 processor which only borrows concepts from ARM (low power consumption, optional compact instruction set etc.), but is otherwise different from an ARM. The Dreamcast also features a sound chip designed by Yamaha with an ARM7 core. Nintendo’s Gameboy Advance, however, uses the ARM7TDMI at 16.78MHz.

DEC licensed the architecture (which caused some confusion because they also produced the DEC Alpha) and produced the StrongARM. At 233 MHz this CPU drew only 1 watt of power (more recent versions draw far less). This work was later passed to Intel as a part of a lawsuit settlement, and Intel took the opportunity to supplement their aging i960 line with the StrongARM. Intel have since developed its own high performance implementation known by the name XScale.

ARM Cores

Thumb

Perhaps in part because of the conditional execution facility using up four bits of every instruction, newer ARM processors have a 16-bit instruction mode, called Thumb. The smaller opcodes have less functionality; for example, only branches can be conditional, and many opcodes cannot access all of the CPU’s registers. However, the shorter opcodes give improved code density overall, even though some operations will require more opcodes to be executed. Particularly in situations where the memory port or bus width is constrained to less than 32 bits, the shorter Thumb opcodes allows greater performance than with 32-bit code because of the more efficient use of the limited memory bandwidth. Typically in embedded applications a small range of addresses have a 32-bit datapath and the rest are 16 bits wide or narrower (e.g. the Game Boy Advance); in this situation, it usually makes sense to compile Thumb code and hand-optimise a few of the most CPU-intensive sections using the 32-bit instruction set, placing them in the limited 32-bit bus width memory.

The first processor with Thumb technology was the ARM7TDMI. All ARM9 and later families, including XScale have included Thumb technology.

Jazelle

ARM has implemented a technology that allows certain of their architectures to execute Java bytecode natively in hardware, in another execution mode alongside the existing ARM and Thumb modes and accessed in a similar fashion to ARM/Thumb interworking.

The first processor with Jazelle technology was the ARM926EJ-S: Jazelle being denoted by the ‘J’ in the CPU name. It has been used by mobile phone manufacturers to speed up execution of Java ME games and applications, which is probably what drove development of the technology.

Thumb-2

Thumb-2 technology made its debut in the ARM1156 core, announced in 2003. Thumb-2 extends the limited 16-bit instruction set of Thumb with additional 32-bit instructions to give the instruction set more breadth. As a result the stated aim for Thumb-2 is to achieve code density that is similar to Thumb with performance similar to the ARM instruction set on 32-bit memory.

Thumb-2 also extends both the ARM and Thumb instruction set with yet more instructions, including bit-field manipulation, table branches, and conditional execution.

Thumb-2EE

Thumb-2EE, marketed as Jazelle RCT, was announced in 2005, first appearing in the Cortex-A8 processor. Thumb-2EE provides a small extension to Thumb-2, making the instruction set particularly suited to code generated at runtime (e.g. by JIT compilation) in managed Execution Environments. Thumb-2EE is a target for languages such as Limbo, Java, C#, Perl and Python, and allows JIT compilers to output smaller compiled code without impacting performance.

New features provided by Thumb-2EE include automatic null pointer checks on every load and store instruction, an instruction to perform an array bounds check, and the ability to branch to handlers, which are small sections of frequently called code, commonly used to implement a feature of a high level language, such as allocating memory for a new object.

NEON

NEON technology is a combined 64 and 128bit SIMD (Single Instruction Multiple Data) instruction set that provides standardized acceleration for media and signal processing applications. NEON can execute MP3 audio decoder on CPU running at 10 MHz and can run the GSM AMR (Adaptive Multi-Rate) speech codec using CPU running at no more than 13 MHz. It features a comprehensive instruction set, separate register files and independent execution hardware. NEON supports 8-, 16-, 32- and 64-bit integer and single precision floating-point data and operates in SIMD operations for handling audio/video processing as well as graphics and gaming processing. SIMD is a crucial element in vector supercomputers which feature simultaneous multiple operations. In NEON, the SIMD supports up to 16 operations at the same time.

VFP

VFP technology is a coprocessor extension to the ARM architecture. It provides low-cost single-precision and double-precision floating-point computation that is fully compliant with the ANSI/IEEE Std 754-1985 Standard for Binary Floating-Point Arithmetic. VFP provides floating-point computation suitable for a wide spectrum of applications such as PDA, smartphones, voice compression and decompression, three-dimensional graphics and digital audio, printers, set-top boxes, and automotive applications. The VFP architecture also supports execution of short vector instructions allowing SIMD (Single Instruction Multiple Data) parallelism. This is useful in graphics and signal-processing applications by reducing code size and increasing throughput.

ARM licensees

ARM Ltd does not manufacture and sell CPU devices based on their own designs, but rather, licenses the processor architecture to interested parties. ARM offers a variety of licensing terms, broken down by cost and deliverables. To all licensees, ARM provides an integratable hardware-description of the ARM core, as well as complete set of software development toolset (compiler, debugger, SDK), and the right to sell manufactured-silicon containing the ARM CPU. Fabless licensees, who wish to integrate an ARM core into their own chip design, are usually only interested in acquiring a ready-to-manufacture, pre-verified IP-core. For these customers, ARM delivers a gate-netlist description of the chosen ARM core, along with an abstracted simulation-model and test programs to aid design integration and verification. More ambitiuous customers, including integrated device manufacturers (IDM) and foundry operators, chose to acquire the processor IP in synthesizable RTL (Verilog) form. With the synthesizable RTL, the customer has the ability to perform architectural level optimizations and extensions. These allow the designer to achieve exotic design goals not otherwise possible with an unmodified netlist (high clock speed, very low power-consumption, instruction-set extensions, etc.) While ARM does not grant the licensee the right to re-sell the ARM-architecture itself, licensees may freely sell manufactured product (chip devices, evaluation boards, complete systems, etc.) Merchant foundries can be a special case; not only are they allowed to sell finished silicon containing ARM-cores, they generally hold the right to re-manufacture ARM-cores for other customers.

Like most IP vendors, ARM prices its IP based on perceived value. In architectural terms, the lower-performance ARM cores command a lower license cost than the higher-performance cores. In terms of silicon implementation, a synthesizable core is more expensive than a hard-macro (black-box) core. Complicating price matters, merchant foundries who hold an ARM license (such as Samsung and Fujitsu) can offer reduced licensing costs to its fab customers. In exchange for acquiring the ARM core through the foundry’s in-house design-services, the customer can reduce or eliminate payment of ARM’s upfront license fee. Compared to dedicated semicounductor foundries (such as TSMC and UMC) without in-house design-services, Fujitsu/Samsung charge 2-3x more per manufactured wafer. For low-mid volume applications, a design-service foundry offers lower overall pricing (through subsidization of the license-fee.) For high volume mass-produced parts, the long-term cost-reduction achievable through lower wafer-pricing reduces the impact of ARM’s NRE cost, making the dedicated foundry a better choice.

Many hightech semiconductor firms hold ARM licenses: Broadcom, Cirrus Logic, Freescale (spun off from Motorola in 2004), Fujitsu, Intel (through its settlement with DEC), IBM, Infineon Technologies, Texas Instruments, Nintendo, Philips, VLSI, Atmel, Sharp, Samsung, and STMicroelectronics are some of the many companies who have licensed the ARM in one form or another. Although ARM’s license terms are covered by NDA, within the IP industry, ARM is widely known to be among the most expensive CPU cores. A single customer product containing a basic ARM-core can incur a one-time license fee in excess of (USD) $200,000. Where significant quantity and architectural modification are involved, the license fee can exceed $10M.

ATMEL Microcontrollers

ATMEL is a manufacturer of semiconductors, founded in 1984. Its focus is on system-level solutions built around flash microcontrollers. Its products include microcontrollers (including 8051 derivatives and AT91SAM ARM-based micros), and its own Atmel AVR and AVR32 architectures, radio frequency (RF) devices, EEPROM and Flash memory devices, and a number of application-specific products. Atmel supplies its devices as standard products, ASICs, or ASSPs depending on the requirements of its customers. In some cases it is able to offer system on chip solutions.

Atmel serves a range of application segments including consumer, communications, computer networking, industrial, medical, automotive, aerospace and military. It is an industry leader in secure systems, notably for the smart card market.

The President and CEO of Atmel is George Perlegos. His brother, Gust Perlegos, is Vice President. There are approximately 8,000 employees currently working for ATMEL, and its market strength is continuing to grow rapidly with it’s introduction of new technologies. It is headquartered in San Jose, California.

Atmel owns five semiconductor facilities which are based in:

* Fab5 in Colorado Springs (USA)

* Fab7 in Rousset (France)

* Fab9 in North Tyneside (England)

* A fab in Heilbronn (Germany)

* A fab in Grenoble (France)

Electronic commutator

How it works

Conventional DC motors employ a mechanical commutator, but new technologies has meant that it is now possible to have an electronic commutator. In both cases, the commutator converts DC into a rotating magnetic field, in order to support continuous rotation. However, the electronic solution affords all the advantages of solid-state construction and operation, plus enables the inherent advantages of brushless motors over their inferior counterparts, without the use of an amplifier. In stark contrast with typical brush DC motor drives, contactors and relays are also eliminated, due to the on-board power supply and built-in directional control.

With the advent of this technological milestone, new levels of performance, efficiency and power density are being made available, with reduced operational and maintenance costs. Applications such as hydraulic power units, integrated starter/alternators, low voltage and small hybrid vehicles, and numerous others, which were previously too complex and expensive, and therefore limited to high end niche markets such as aerospace and military platforms, are now commercially viable.

A brushless motor drive typically consists of two parts – the motor and the amplifier. A motor with an electronics commutator integrates the essential electronics with the motor this approach enables the motor to utilize an industry-standard DC controller. The result is a brushless motor that operates with the simplicity of a DC motor.

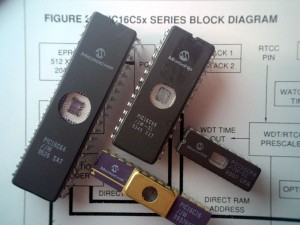

Introducing the PICmicro from Microchip technology

PIC is a family of RISC microcontrollers made by Microchip Technology, derived from the PIC1650 originally developed by General Instrument’s Microelectronics Division.

Microchip Technology does not use PIC as an acronym; in fact the brand name is PICmicro. It is generally regarded that PIC stands for Peripheral Interface Controller, although General Instruments’ original acronym for the PIC1650 was “Programmable Intelligent Computer”. The original PIC was built to be used with GI’s new 16-bit CPU, the CP1600. While generally a good CPU, the CP1600 had poor I/O performance, and the 8-bit PIC was developed in 1975 to improve performance of the overall system by offloading I/O tasks from the CPU. The PIC used simple microcode stored in ROM to perform its tasks, and although the term wasn’t used at the time, it is a RISC design that runs one instruction per cycle (4 oscillator cycles).

In 1985 General Instruments spun off their microelectronics division, and the new ownership cancelled almost everything — which by this time was mostly out-of-date. The PIC, however, was upgraded with EPROM to produce a programmable channel controller, and today a huge variety of PICs are available with various on-board peripherals (serial communication modules, UARTs, motor control kernels, LCD drivers, etc.) and program memory from 512 words to 32k words and more (a “word” is one assembly language instruction, varying from 12, 14 or 16 bits depending on the specific PICmicro family).

Writing Code for PICs

PICs use a RISC instruction set, which varies in length from about 35 instructions for the low-end PICs to about 70 instructions for the high-end PICs. The instruction set includes instructions to perform a variety of operations on the accumulator and a constant or the accumulator and a memory location, as well as for conditionally executing code and jumping/calling other parts of the program and returning from them, and specific hardware features like interrupts and one low-power mode called sleep. Microchip provides a freeware IDE package called MPLAB, that also includes a software simulator as well as an assembler.

Third parties make C and BASIC language compilers for PICs. Microchip also sells compilers for the high-end PICs (“C18” for the 18F series and “C30” for the dsPICs). They also make available for download a “student edition/demo” version of C18 or C30 which disables some optimiser features after a timeout period. Open-source compilers for the C, Pascal, JAL, and for the Forth programming language, PicForth, have also been released.

GPUTILS is an Open Source collection of tools, distributed under the GNU General Public License. GPUTILS includes an assembler and linker and works on Linux, Mac OS X, OS/2 and Microsoft Windows. GPSIM is an Open Source simulator for the PIC microcontrollers featuring hardware modules that simulate specific devices that might be connected to them, like LCDs.

Devices called “programmers” are traditionally used to get program code into the target PIC. Most PICs that Microchip sells nowadays have ICSP (In Circuit Serial Programming) and/or LVP (Low Voltage Programming) capabilities, allowing the PIC to be programmed while it is sitting in the target circuit. ICSP programming is performed using the RB6 and RB7 pins for clock and data, while a high voltage (12V) is present on the Vpp/MCLR pin. Low voltage programming allows for the elimination of the extra voltage rail in the programmer but comes at the cost of an IO pin and can therefore be disabled (once disabled it can only be re-enabled using high voltage programming). There are many programmers for PIC microcontrollers, ranging from the extremely simple designs that rely on the communications software for taking care of all the communication details to complex designs that can verify the device at several supply voltages and can do much of the work in the hardware. Many of these complex programmers use a pre-programmed PIC themselves to send the programming commands to the PIC that is to be programmed.

Many of the higher end flash based PICs can also write to their own program memory. Demo boards are available with a small bootloader factory programmed that can be used to load user programs over an interface such as RS-232 or USB.

There are many programmers/debuggers available directly from Microchip:

- PICStart Plus (RS232 serial interface)

- Promate II (RS232 serial interface)

- MPLAB PM3 (RS232 serial and USB interface)

- ICD2 (RS232 serial and USB interface)

- PICKit 1 (USB interface)

- PICKit 2 (USB interface)

Debugging

MPLAB (which is a free download) includes a software emulator for PICs. However software emulation of a microcontroller will always suffer from limited simulation of the devices interactions with its target circuit.

The MPLAB ICD2 (RS-232 serial and USB interface). Offers fairly cheap (about £100) in circuit debugging. A programming/debug connector (the ICD2 has a RJ12 socket and comes with a cross wired RJ12 lead but there is nothing preventing the use of custom cables to other connector types) is designed into the target circuit. This cheap and simple debugging system comes at a price however, namely limited breakpoint count (1 on older pics 3 on newer PICs), loss of some IO (with the exception of some surface mount 44 pin PICs which have dedicated lines for debugging) and loss of some features of the chip. For small PICs where the loss of IO caused by this method would be unacceptable special headers are made which are fitted with PICs that have extra pins specifically for debugging. Some third party debugging solutions also exist using the on chip facilities provided for the ICD2.

Finally microchip offers two full in circuit emulators. The MPLAB ICE2000 (parallel interface, a USB converter is available) and the newer MPLAB ICE4000 (USB interface). There are also third party emulators from such companies as RF Solutions, who produce the ICEPIC3 system, these are often lower cost solutions.

Word size

The word size of PICs is a source of much confusion. All PICs (except dsPICs and PIC24s) handle data in 8-bit chunks, so they should be called 8-bit microcontrollers. But unlike most CPUs, PICs use Harvard architecture, so the size of an instruction can be different from the size of the data. In fact, different PIC families use different instruction sizes, which makes it a challenge to compare the code size of PICs to other microcontrollers. For example, say a microcontroller has 6144 bytes of program memory. For a 12-bit PIC, this works out to 4096 words (or assembly instructions); for a 16-bit PIC, this is 3072 words.

Modern PICs

The old PROM and EPROM PICs are now gradually replaced by chips with Flash memory. Likewise the original 12-bit instruction set of the PIC1650 and its direct descendants has been superseded by 14-bit and 16-bit instruction sets. Microchip still sells OTP (one-time-programmable, or PROM) and UV-eraseable (EPROM) versions of most of its PICs for legacy support, or volume orders. It should be noted that the Microchip website lists PICs that are not electrically erasable as OTP despite the fact that UV erasable windowed versions of these chips can be ordered.

Features

Current PICs offer a wide range of built-in hardware, such as:

- 8/16 bit Modified Harvard Architecture CPU cores

- Flash and ROM Memory options in 256 byte to 256 kilobyte array sizes

- I/O Ports (0 to 5.5 volts Typical)

- 8/16 Bit Timers

- Nanowatt Technology for Power Moding

- Synchronous/Asynchronous Serial Peripherals USART, AUSART, EUSARTs

- Analog-to-digital converters, 10/12 bit

- Voltage Comparators

- Capture/Compare/PWM modules

- LCD Drivers

- MSSP Peripheral for I²C and SPI Communications

- Internal EEPROM Memory – up to 1M erase/write cycles durability

- Motor Control Peripherals

- USB interfacing support

- Ethernet controller support

- CAN controller support

- LIN controller support

- IrDA controller support

- Integrated analog RF front ends (PIC16F639, and rfPIC)

- KEELOQ Rolling code encryption peripheral (encode/decode)

- DSP digital signal processing capabilities (dsPIC)

PICs on the Internet

PICs are well-documented on the Internet, mainly for two reasons. First, PICs were commonly used to defeat the security system of popular consumer products (pay-TV, PlayStation), which attracted the attention of crackers. Second, the now obsolete PIC16C84 was the first widely available microcontroller that could easily be re-programmed by hobbyists. There are many forums and lists concerning PIC microcontrollers where the user can post questions and receive free answers.

PIC clones

Every now and then there are companies that offer cheap and/or enhanced PIC versions. Most seem to disappear quite soon. Ubicom (formerly Scenix) seems to avoid this fate and produces the SX, a PIC clone that runs much faster than the original (as of November 2005 Parallax is the exclusive supplier of the SX). OpenCores has a pic16f84 core written in Verilog.

Wireless PICs

The rfPIC microcontroller devices integrate the power of Microchip´s PICmicro devices with UHF wireless communication capabilities for low power RF applications. The devices offer small package outline and low external component count to fit the most space-constrained applications.

dsPICs (Digital Signal PICs)

dsPICs are Microchip’s newest family, which entered mass production in late 2004. They are designed as a PIC with digital signal processing capabilities. These are Microchip’s first inherent 16-bit (data) microcontrollers. They build on the PICs existing strengths by offering hardware MAC (multiply-accumulate), barrel shifting, bit reversal, (16×16)-bit multiplication and other digital signal processing operations.

8/16-bit PIC microcontroller product families

These links take you to product selection matrices at the manufacturer’s site.

8-bit Microcontrollers

- PIC10

- PIC12

- PIC14

- PIC16

- PIC17

- PIC18

16-bit Microcontrollers

- PIC24

16-bit Digital Signal Controllers

- dsPIC30

- dsPIC33F

The F in a name generally indicates the PICmicro uses flash memory and can be erased electronically. A C generally means it can only be erased by exposing the die to ultraviolet light (which is only possible if a windowed package style is used).

External links

For more information visit www.Microchip.com

Linux PIC Programmer Software

PICPrg A fast Linux command line (or ncurses) program, to program any Microchip PIC using the PC parallel port interface. Program/verify PIC data, erase non-protected/protected PIC data or calculate the PIC checksum.